Summary

CompuLab Intense PC and MintBox 2 fail to properly write protect flash regions, allowing an attacker with local administrator privileges to write arbitrary code to the platform firmware. This could allow a remote attacker to install a persistent firmware level rootkit to the computer, or to erase the system firmware, causing a denial of service.

Installation of a modified firmware can occur entirely in the background, without any user interaction, and once performed is virtually impossible to difficult to detect using operating system utilities. Physical access is not required.

Product description

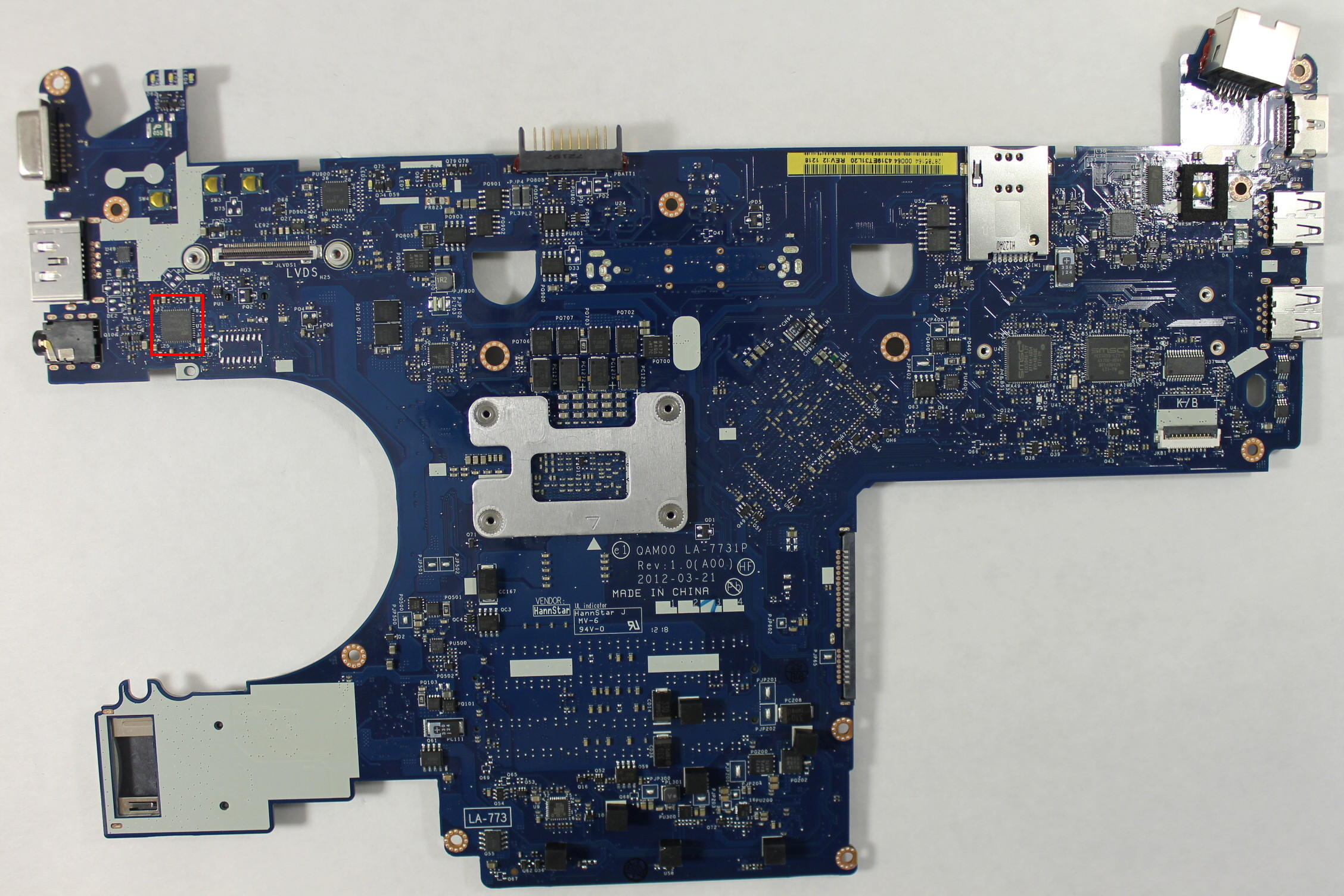

The CompuLab Intense PC is fanless mini-PC. A model pre-installed with Linux Mint is also marketed under the name MintBox 2. The system firmware is the same for the Intense PC and MintBox 2. CompuLab also sell the Intense PC with an extended temperature range for industrial applications.

The product was introduced in mid-2013 and is still being sold through Amazon US, Amazon Canada, Amazon Germany, Amazon Spain, and directly from CompuLab.

Affected products

- Intense PC (Intense PC Value, Intense PC Business, Intense PC Pro)

- MintBox 2

At the time of discovery in March 2017, the latest firmware for CompuLab was dated 21 June 2016, and did not enable write protection on any flash regions.

Impact

Any software running with local administrator privileges has unrestricted access to read and write the system’s firmware.

An attacker can modify the contents of the system firmware to install a persistent rootkit/bootkit, or to corrupt the firmware causing the computer to cease functioning.

The attack only requires local administrator privileges, and can be executed either by using an existing OS-level exploit to gain local administrator, or via tricking the user into running an executable (e.g. via an attachment in a phishing email).

Proof of Concept

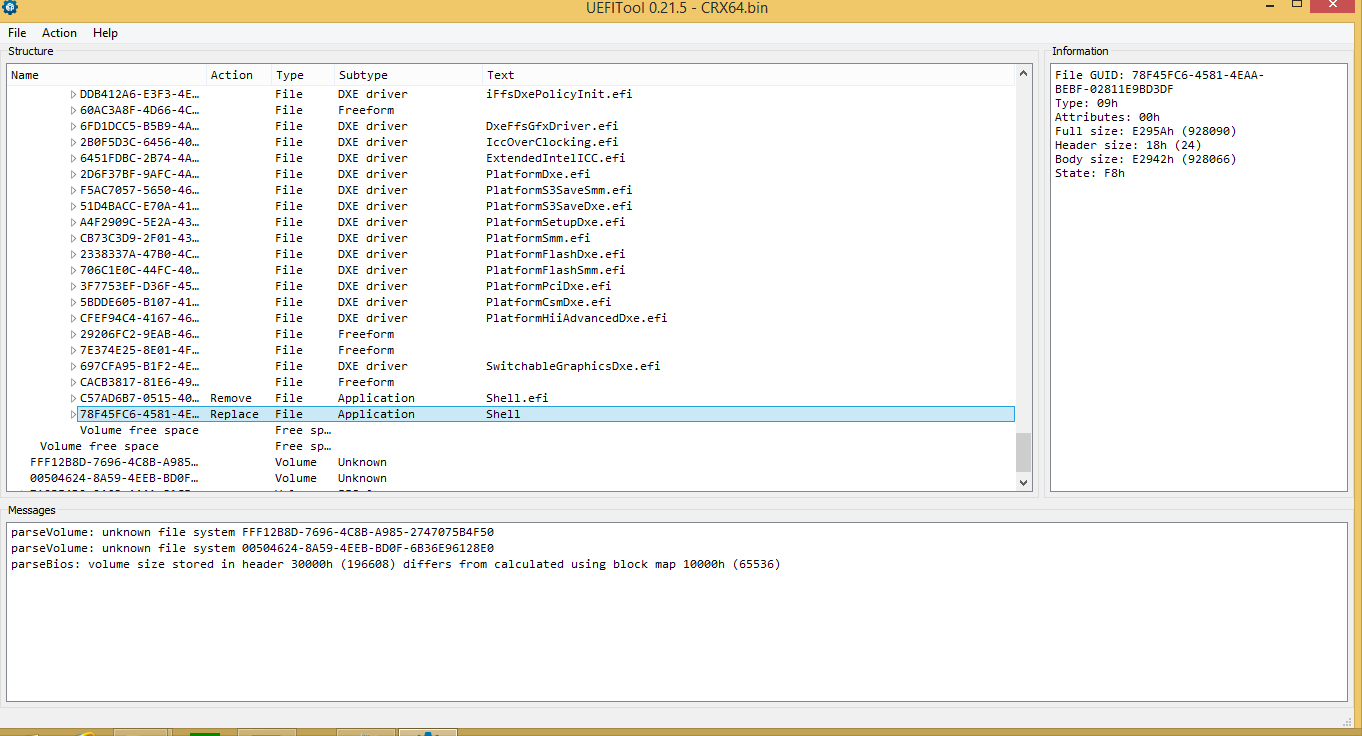

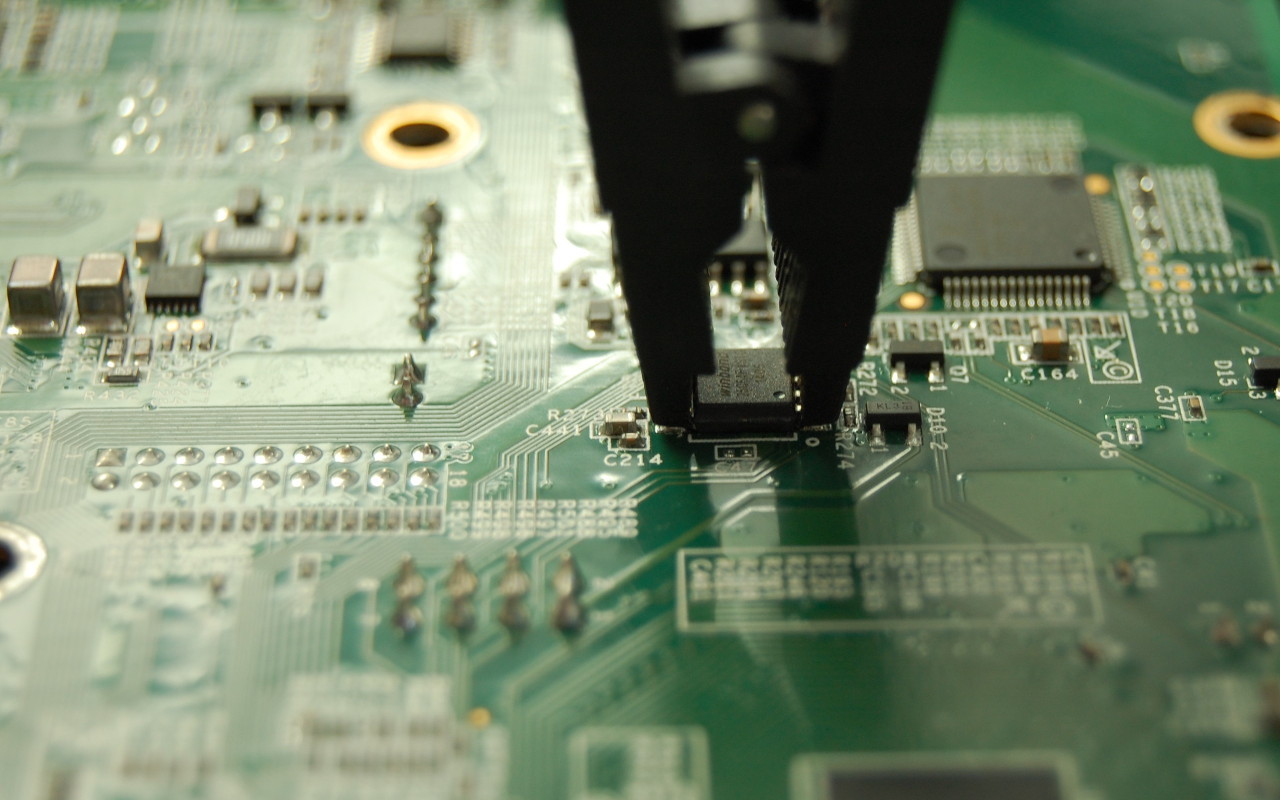

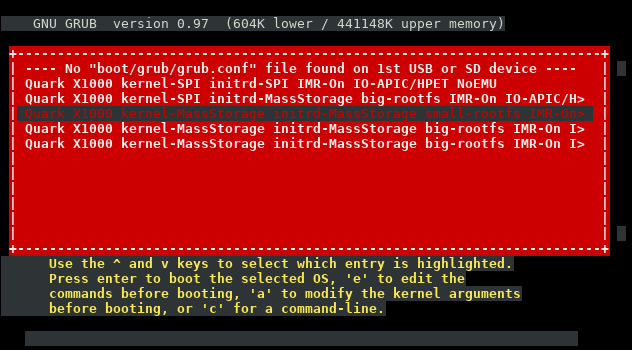

The firmware update from CompuLab was downloaded, decompressed, and loaded into UEFITool.

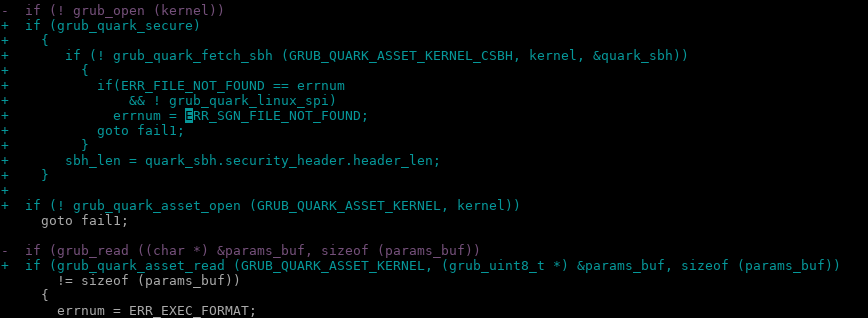

The default UEFI shell provided in Phoenix SecureCore was replaced with a newer version of the UEFI shell from EDK2:

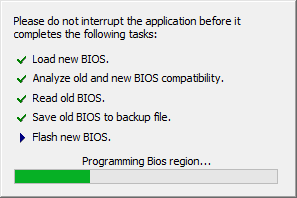

The modified update was then written to the system firmware using the Phoenix UEFI Winflash utility:

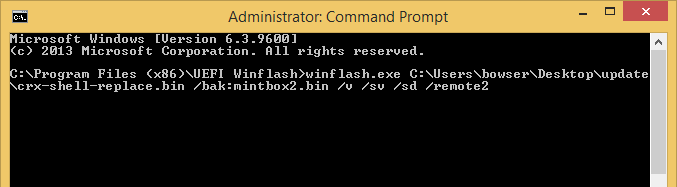

It was later realized that the Phoenix UEFI Winflash utility includes a flag enabling a silent firmware update from the command line:

Using the /remote2 option removes all visual notifications that a firmware update is in progress. Additionally, when used with /console or /remote2 options, the Winflash utility does not reboot the platform when finished. The system continues to function normally, and there is no indication to the user that a firmware update has taken place at all.

Additional information

Output of the chipsec utility:

python chipsec_main.py -m common.bios_wp

################################################################

## ##

## CHIPSEC: Platform Hardware Security Assessment Framework ##

## ##

################################################################

[CHIPSEC] Version 1.3.0

[CHIPSEC] Arguments: -m common.bios_wpWARNING: *******************************************************************

WARNING: Chipsec should only be used on test systems!

WARNING: It should not be installed/deployed on production end-user systems.

WARNING: See WARNING.txt

WARNING: *******************************************************************[CHIPSEC] API mode: using CHIPSEC kernel module API

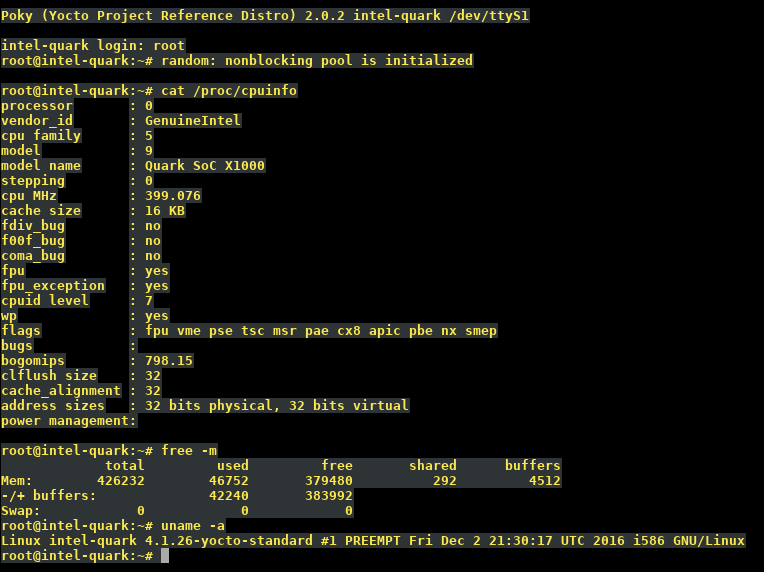

[CHIPSEC] OS : Windows 8.1 6.3.9600 AMD64

[CHIPSEC] Platform: Mobile 3rd Generation Core Processor (Ivy Bridge CPU / Panth

er Point PCH)

[CHIPSEC] VID: 8086

[CHIPSEC] DID: 0154[+] loaded chipsec.modules.common.bios_wp

[*] running loaded modules ..[*] running module: chipsec.modules.common.bios_wp

[x][ =======================================================================

[x][ Module: BIOS Region Write Protection

[x][ =======================================================================

[*] BC = 0x08 << BIOS Control (b:d.f 00:31.0 + 0xDC)

[00] BIOSWE = 0 << BIOS Write Enable

[01] BLE = 0 << BIOS Lock Enable

[02] SRC = 2 << SPI Read Configuration

[04] TSS = 0 << Top Swap Status

[05] SMM_BWP = 0 << SMM BIOS Write Protection

[-] BIOS region write protection is disabled![*] BIOS Region: Base = 0x00D00000, Limit = 0x00FFFFFF

SPI Protected Ranges

————————————————————

PRx (offset) | Value | Base | Limit | WP? | RP?

————————————————————

PR0 (74) | 00000000 | 00000000 | 00000000 | 0 | 0

PR1 (78) | 00000000 | 00000000 | 00000000 | 0 | 0

PR2 (7C) | 00000000 | 00000000 | 00000000 | 0 | 0

PR3 (80) | 00000000 | 00000000 | 00000000 | 0 | 0

PR4 (84) | 00000000 | 00000000 | 00000000 | 0 | 0[!] None of the SPI protected ranges write-protect BIOS region

[!] BIOS should enable all available SMM based write protection mechanisms or co

nfigure SPI protected ranges to protect the entire BIOS region

[-] FAILED: BIOS is NOT protected completely

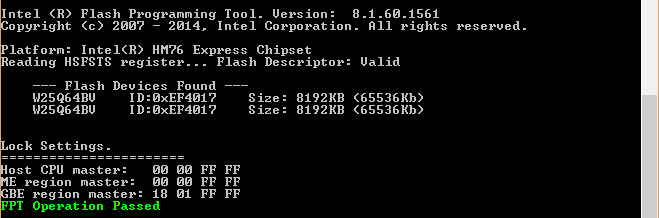

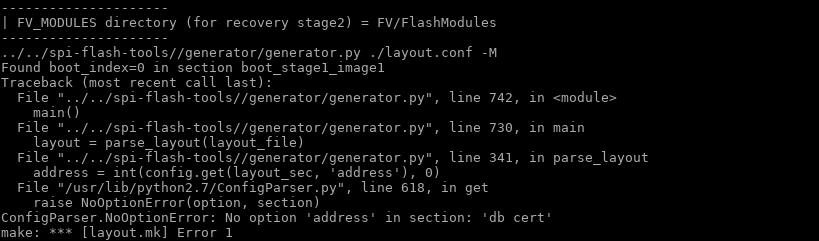

Output of the Intel Flash Programming Tool (FPT):

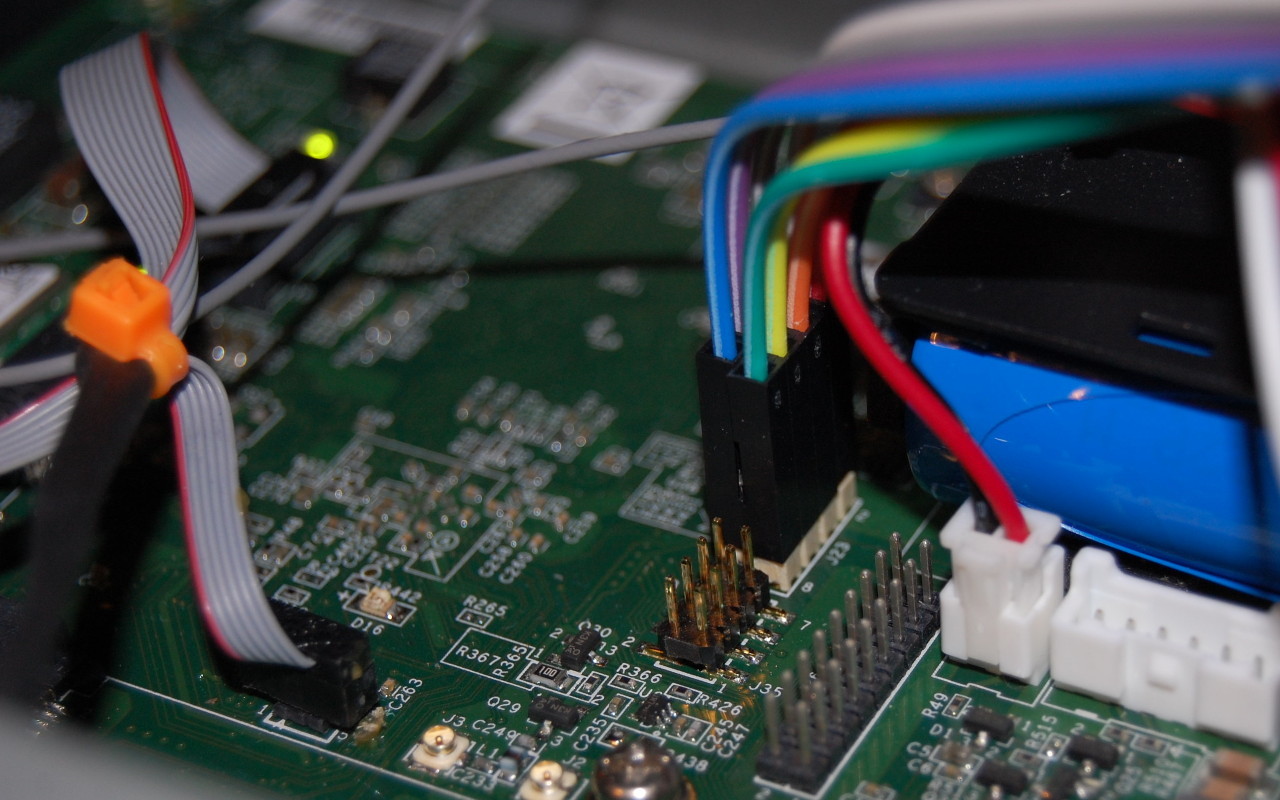

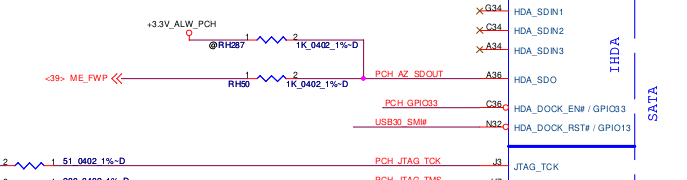

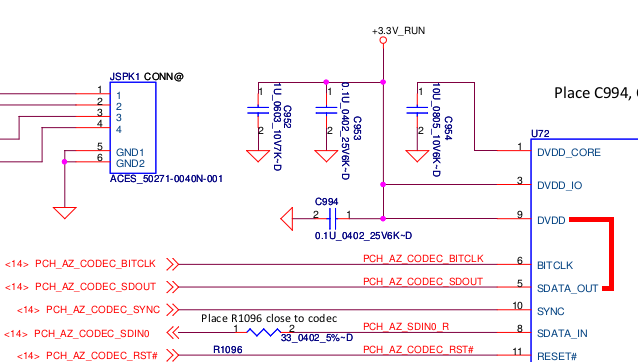

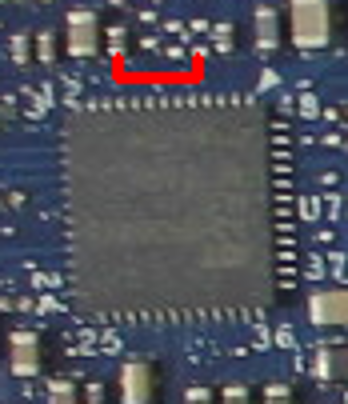

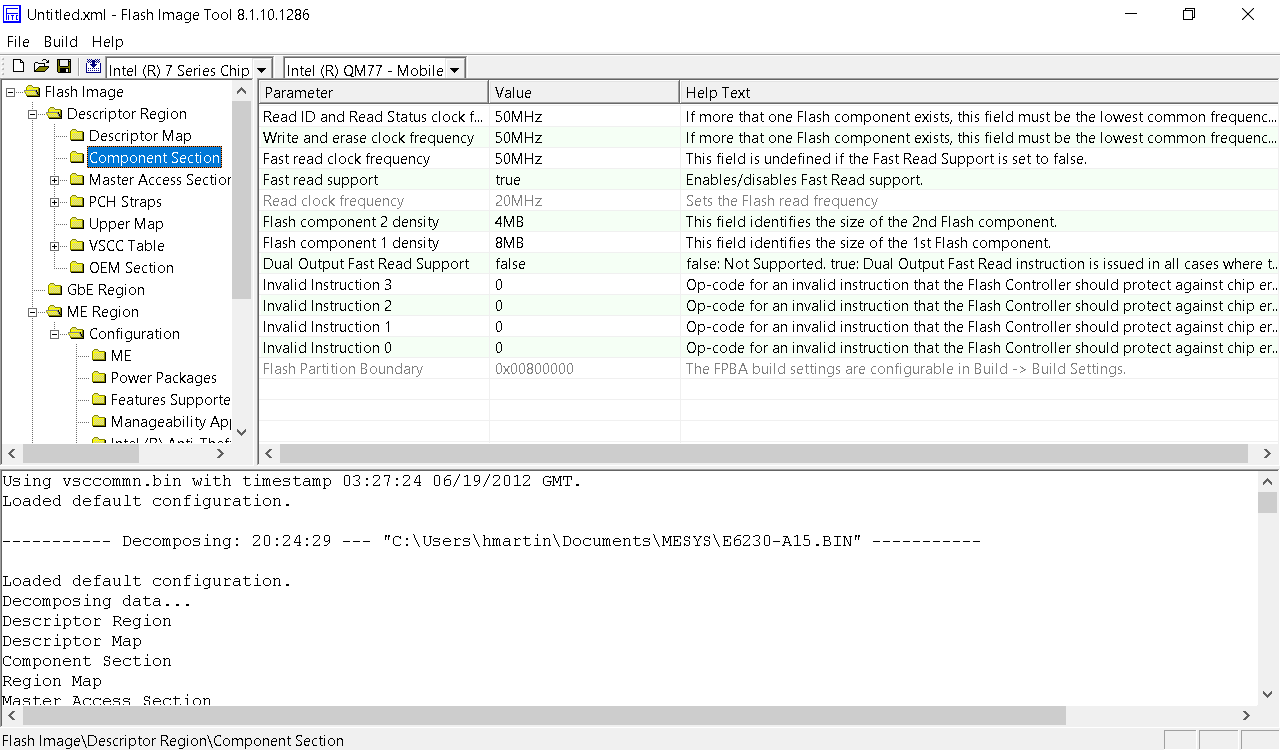

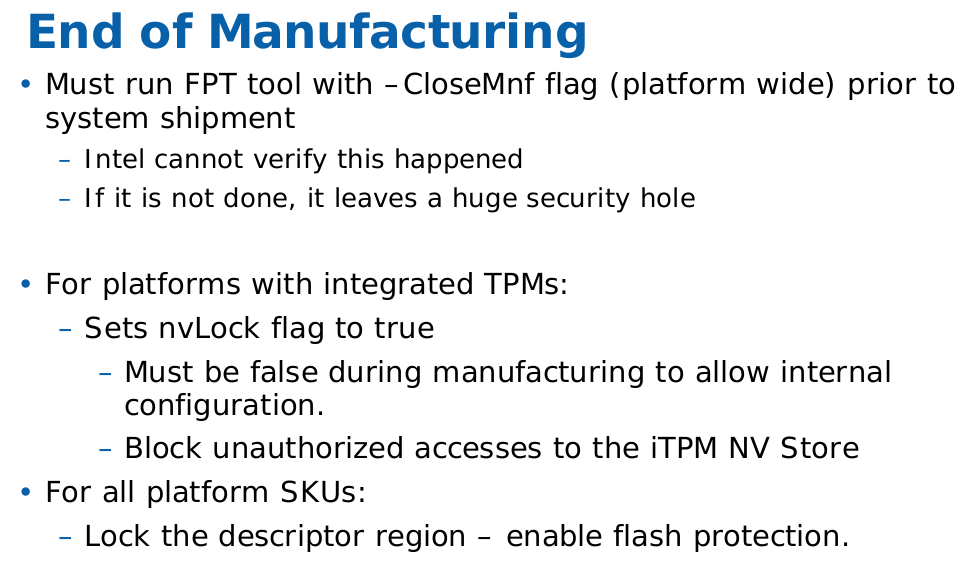

Through my discussion with CompuLab support, it has emerged that the issue is due to CompuLab not running CloseMnf prior to shipping. CloseMnf stands for “Close of Manufacturing” and hardens the system by setting write-protect flags for the various flash regions in the Master Access Section of the Descriptor Region.

Intel documentation regarding CloseMnf:

Disclosure timeline:

1 March 2017: Vulnerability is reported to CompuLab via their support email address

2 March 2017: CompuLab replies they will create a beta BIOS to address the vulnerability

6 March 2017: I request a timeline to fix the issue

7 March 2017: CompuLab replies they will create a beta BIOS for testing and they “will provide an official public release in the future”

8 March 2017: CompuLab replies with instructions to run closemnf via the Intel FPT tool

8 March 2017: I inform CompuLab I am waiting for the official BIOS update to resolve the issue

8 March 2017: CompuLab replies with copy of Intel FPT tool and requests “not to publish or disclose this information”

8 March 2017: CompuLab is informed that details of the vulnerability will be published on 4 June 2017

23 April 2017: Issue is reported to MITRE

24 April 2017: Vulnerability is assigned CVE-2017-8083

3 May 2017: CompuLab communicates that they will delay fixing this vulnerability until Intel provides an updated ME firmware to address CVE-2017-5689

4 May 2017: I inform CompuLab that details of this vulnerability will be published on 4 June 2017 as previously discussed

11 May 2017: CompuLab sends a proposed fix for testing, the update script fails due to invalid command syntax for flashrom

14 May 2017: I inform CompuLab of the invalid syntax and provide the correct usage, and confirm that the fix enables write-protection on the ME/BIOS/GbE regions of flash

15 May 2017: CompuLab replies with a revised update script

15 May 2017: I inform CompuLab that the syntax of the revised script is correct, however my unit has already been updated so I cannot re-test

4 June 2017: Details of the vulnerability are published.

CompuLab have provided an update to address the issue.

I can confirm that the Phoenix update utility still functions so it is still possible to update the BIOS even after the FDR has been locked.